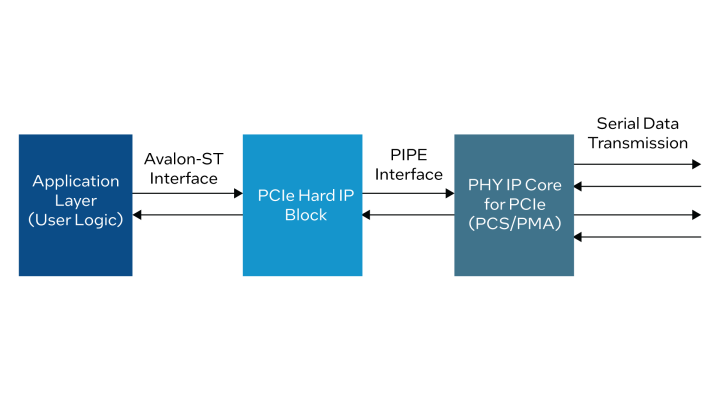

PIPE SerDes Architecture for PCIe Gen 5 and Beyond - Verification - Cadence Blogs - Cadence Community

PCIe Gen4 Standards Margin-Assisted Outer-Layer Equalization for Cross-Lane Optimization in a 16GT/s PCIe Link | 2018-11-09 | Signal Integrity Journal

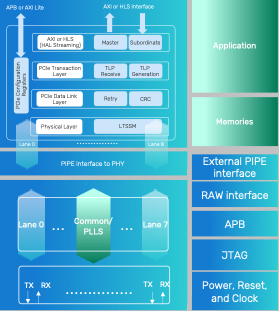

PCIe 6.0 Standard Ratified...and Cadence's Implementation - Breakfast Bytes - Cadence Blogs - Cadence Community

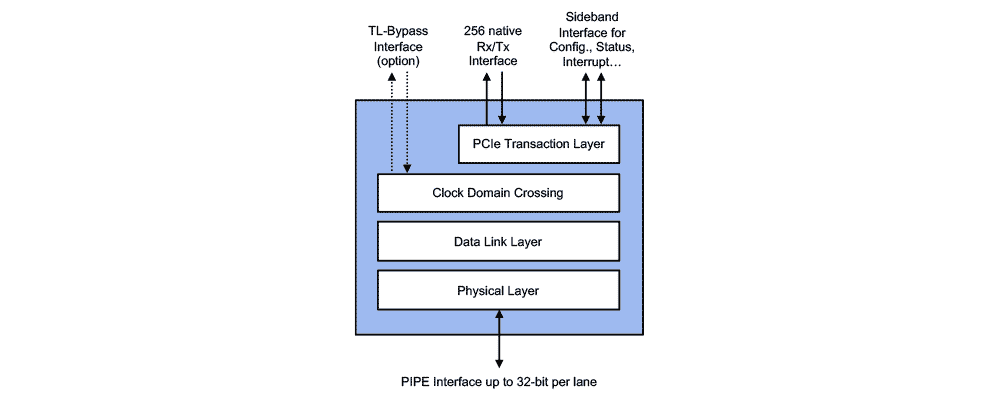

Demystifying PIPE interface packets using the in-built descrambler module in UltraScale+ Devices Integrated Block for PCI Express Gen3